Objective

My passion lies in pursuing high impact innovation, and my talent lies in being able to link the full innovation stack, from understanding which problem to solve, bringing out the best ideas in others, identifying unconventional ideas and approaches, securing stakeholder buy-in and resources, leading the design team to successful implementation, test & validation, report-out, and refining to industrial maturity.

I fit well in any R&D program looking for strategic risk taking and independent thinking. My background is in analog and mixed signal IC design, especially ADCs. More recently, I have expanded my research interests to include AI and Machine Learning. This combination of skills and perspective, spanning Computer Science and Electrical Engineering aspects of the innovation landscape, puts me in a strong position to bring unique insight and diversity of thought – whether circuits-focused, algorithms-focused, or both.

Experience

2023 – current Analog Engineer at Intel USA

Innovating solutions for next generation 448Gbps SerDes in angstrom-scale CMOS process technologies.

2022 – 2022 Principal Engineer at Infinera USA

Contributed to the design of ADCs, DACs, and PLLs in 5nm CMOS for optical transceivers operating in the tens to hundreds of giga-samples. Strong exposure to product design principles and practices.

2013 – 2020 Principal Scientist at imec Leuven, Belgium

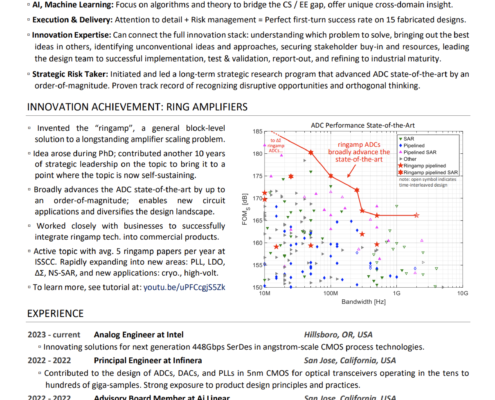

Lead research efforts in next-generation technologies for analog, mixed-signal, and RF integrated circuits spanning the wireless receiver chain, from the RF frontend down to the ADC. These projects are described on my projects page. Redefined the ADC performance and power efficiency state of the art and delivered an order-of-magnitude breakthrough in direct-RF sampling ADCs by harnessing the capabilities of ring amplifiers. Evolved ringamp technology from prototype to mature solution and helped customers integrate into commercial products. Worked extensively with 16nm FinFET, 28nm planar CMOS, and 180nm RF SOI technologies.

2006 – 2012 Graduate Student at Oregon State University Corvallis, Oregon, USA

Conducted PhD research focused on scalable amplification solutions for switched capacitor circuits. Invented the the concept of ring amplification, which has reshaped the state-of-the-art and design landscape in the last decade, and continues to grow as a topic. Designed and fabricated four pipelined ADCs, described on my projects page. All chips worked on the first attempt, and highlights include two consecutive state-of-the-art benchmarks for efficiency in high resolution ADCs. Followed advanced graduate courses in mixed-signal IC design, RF, filters, PLLs, delta-sigma, circuit simulators, and device physics. Advisor: Dr. Un-Ku Moon

2003 – 2012 Freelance Web Developer Corvallis, Oregon, USA

Ran a web design business to fund college education, with 3 employees. Strong programming and software engineering background. Enterprise clients include the IEEE Magnetics Society, DAMA International, and Portland, OR law firms.

Publication

Papers

A full list of downloadable papers is available on my publications page.

You can also find me on google scholar.

Selected publications:

Ring Amplifiers for Switched Capacitor Circuits

B. Hershberg, S. Weaver, K. Sobue, S. Takeuchi, K. Hamashita, and U. Moon

In Solid-State Circuits, IEEE Journal of, Dec, 2012.

» [Paper] [DOI] [Abstract] [Bibtex]

@ARTICLE{2012-jssc-ringamp,

author={Hershberg, B. and Weaver, S. and Sobue, K. and Takeuchi, S. and Hamashita, K. and Un-Ku Moon},

journal={{Solid-State Circuits, IEEE Journal of}},

title={{Ring Amplifiers for Switched Capacitor Circuits}},

year={2012},

month={Dec},

volume={47},

number={12},

pages={2928-2942},

abstract={In this paper the fundamental concept of ring amplification is introduced and explored. Ring amplifiers enable efficient amplification in scaled environments, and possess the benefits of efficient slew-based charging, rapid stabilization, compression-immunity (inherent rail-to-rail output swing), and performance that scales with process technology. A basic operational theory is established, and the core benefits of this technique are identified. Measured results from two separate ring amplifier based pipelined ADCs are presented. The first prototype IC, a simple 10.5-bit, 61.5 dB SNDR pipelined ADC which uses only ring amplifiers, is used to demonstrate the core benefits. The second fabricated IC presented is a high-resolution pipelined ADC which employs the technique of Split-CLS to perform efficient, accurate amplification aided by ring amplifiers. The 15-bit ADC is implemented in a 0.18 μm CMOS technology and achieves 76.8 dB SNDR and 95.4 dB SFDR at 20 Msps while consuming 5.1 mW, achieving a FoM of 45 fJ/conversion-step.},

keywords={CMOS analogue integrated circuits;amplifiers;analogue-digital conversion;CMOS technology;SNDR pipelined ADC;Split-CLS;compression-immunity;power 5.1 mW;rapid stabilization;ring amplification;ring amplifier;size 0.18 micron;slew-based charging;switched capacitor circuit;word length 10.5 bit;word length 15 bit;Accuracy;CMOS integrated circuits;Gain;Inverters;Ring oscillators;Stability analysis;Transistors;A/D;ADC;CLS;RAMP;analog to digital conversion;analog to digital converter;correlated level shifting;high resolution;low power;nanoscale CMOS;rail-to-rail;ring amp;ring amplification;ring amplifier;ringamp;scalability;scaling;slew-based;split-CLS;stabilized ring oscillator;switched capacitor},

doi={10.1109/JSSC.2012.2217865},

ISSN={0018-9200},

type={journal},} A 4-GS/s 10-ENOB 75-mW Ringamp ADC in 16-nm CMOS With Background Monitoring of Distortion

B. Hershberg, D. Dermit, B. van Liempd, E. Martens, N. Markulić, J. Lagos, and J. Craninckx

In IEEE Journal of Solid-State Circuits, Aug, 2021.

» [Paper] [DOI] [Abstract] [Bibtex]

@ARTICLE{2021-jssc-type1-direct-rf-ringamp,

author={Hershberg, Benjamin and Dermit, Davide and van Liempd, Barend and Martens, Ewout and Markulić, Nereo and Lagos, Jorge and Craninckx, Jan},

journal={{IEEE Journal of Solid-State Circuits}},

title={{A 4-GS/s 10-ENOB 75-mW Ringamp ADC in 16-nm CMOS With Background Monitoring of Distortion}},

year={2021},

volume={56},

number={8},

pages={2360-2374},

abstract={A 4x interleaved pipelined ADC for direct-RF sampling applications is presented. It leverages the performance advantages of ring amplifiers to unlock greater architectural freedom. The first pipeline stage MDAC with a “passive-hold” mode eliminates the sub-ADC sampling path and associated problems. A high-speed ringamp topology employs digital bias control, robust common-mode feedback (CMFB), and an elegant self-resetting behavior. An asynchronous, event-driven timing control system improves several aspects of performance and enables fully dynamic power consumption and modular design re-use. A general technique is presented whereby the signal-to-distortion ratio (SDR) of any amplifier in the system can be measured in the background with an analog hardware overhead of only one comparator. In this amplifier-intensive architecture utilizing 36 ringamps, the 4-GS/s ADC fabricated in 16-nm CMOS achieves 62-dB SNDR and 75-dB SFDR at Nyquist, consumes 75 mW (including input buffer), and has a Walden figure of merit (FoM) of 18 fJ/conversion-step and a Schreier FoM of 166 dB, advancing the state of the art in direct-RF sampling ADCs by roughly an order of magnitude.},

keywords={},

doi={10.1109/JSSC.2021.3053893},

ISSN={1558-173X},

month={Aug},

type={journal}}Academic Engagement

Regular peer reviewer for:

IEEE Journal of Solid State Circuits (JSSC)

IEEE Transactions on Circuits and Systems (TCAS)

IEEE Symposium on VLSI Technology and Circuits (VLSI)

IEEE Intl. Solid State Circuits Conference (ISSCC)

IEEE Electronic Letters

IEEE Transactions on VLSI Systems (TVLSI)

Patents

US 10484000 B2

US 10574255 B2

US 10536159 B2

US 10090852 B2

US 9948446

US 10230347 B2

US 9979376

US 11271580

+2 patents pending

Education

PhD, Electrical Engineering, 2012

BS Honors, Electrical Engineering, 2006

BS Honors, Computer Engineering, 2006

Minor, Computer Science, 2006

All degrees granted by

Oregon State University, Corvallis, USA

Awards and Honors

- 2023 IEEE Paul Brokaw Award for Circuit Elegance

- ISSCC 2019 Lewis Winner Award for Outstanding Paper*

- 2010 Analog Devices Student Design Award recipient

- 2012 Broadcom University Research Competition winner (2nd place)

* This is the “best paper” award of ISSCC, the #1 ranked conference in the field of Solid State Circuits.

- AACD 2014 Invited Lecturer

- ISSCC 2020 Invited Lecturer

- CICC 2020 Invited Lecturer

References

Available upon request.